申请日2017.12.06

公开(公告)日2018.06.19

IPC分类号G06F9/30

摘要

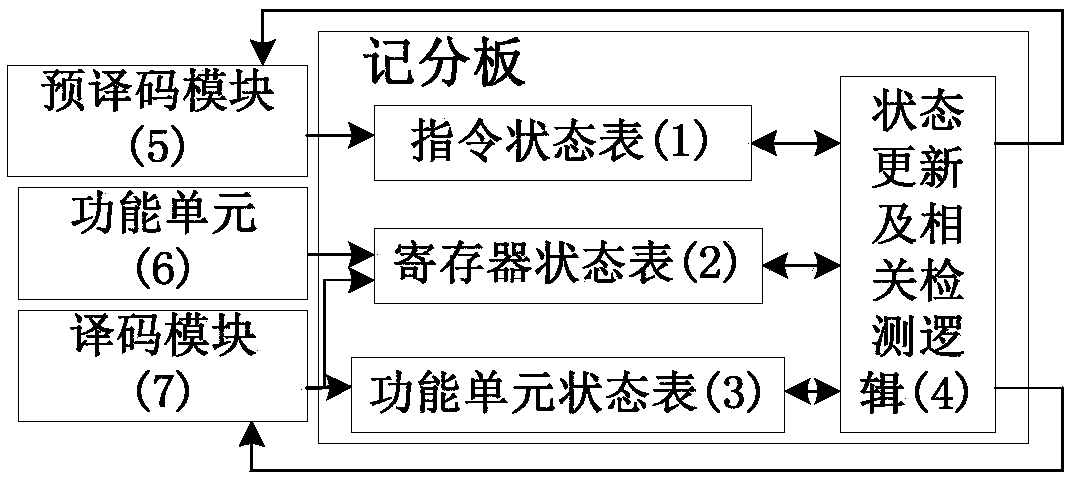

本发明属于集成电路技术领域,涉及一种流水处理双发射处理器记分板电路,包括:指令状态表1、寄存器状态表2、功能单元状态表3和状态更新及相关检测逻辑4。本发明能够根据预译码模块提供的两条待发射指令的信息、译码模块提供的两条发射指令的信息以及各个功能单元提供的指令执行完毕的信息,来记录指令、功能单元和寄存器三个状态表,使用上述三个状态表信息,在预译码单元5发出两条指令的同时,流水检测待发射指令与正在执行指令之间是否存在数据相关、功能单元相关和写回通路相关,并为预译码单元5和译码单元7返回指令是否准备好的信息。

权利要求书

1.一种流水处理双发射处理器记分板电路,其特征在于:包括:

指令状态表(1)、寄存器状态表(2)、功能单元状态表(3)和状态更新及相关检测逻辑(4);

指令状态表(1)接受预译码模块(5)中取出的两条待发射指令的对应数据,将数据处理为如下信息:源寄存器、目的寄存器、源操作数ready、目的操作数ready、该指令在执行级所需周期数、所使用操作单元,将所述信息发送至状态更新及相关检测逻辑(4);

寄存器状态表(2)接收功能单元(6)和译码模块(7)的数据,将数据处理为模块使用到的64个寄存器的状态信息,所述状态信息表示64个寄存器是否因正在使用而被锁定,将状态信息发送至状态更新及相关检测逻辑(4);

功能单元状态表(3)接收译码模块(7)的数据,将数据处理为所有执行部件的使用状态信息,包括:该功能单元是否有任务运行和每个任务距离寄存器写回操作的周期数,将所述使用状态信息发送至状态更新及相关检测逻辑(4);

状态更新及相关检测逻辑(4)根据指令状态表(1)、寄存器状态表(2)、功能单元状态表(3)发送的信息共同判断两条待发射指令和正在执行的指令之间是否存在数据相关、功能单元相关或写回通路相关,若三种相关均不存在即可将待发射指令判断为指令准备好。

2.根据权利要求1所述的流水处理双发射处理器记分板电路,其特征在于:状态更新及相关检测逻辑(4)在进行待发射指令与正在执行指令是否存在写回通路相关的判断时,不仅要将待发射指令状态与当前时钟周期正在执行指令的状态进行比较,还要进行下一周期是否相关的预测。

3.根据权利要求1所述的流水处理双发射处理器记分板电路,其特征在于:状态更新及相关检测逻辑(4)中所述相关判断均要在同一周期内完成。

4.根据权利要求1所述的流水处理双发射处理器记分板电路,其特征在于:状态更新及相关检测逻辑(4)中判断的两条待发射指令均与正在执行的指令若不相关时,便在下一周期将两条指令同时下发,该情况下支持流水操作;若仅有一条指令与正在执行的指令不相关,下一周期即可下发一条指令,若两条指令均与正在执行的指令存在相关则等到指令准备好再下发,该两种情况将打断流水周期。

说明书

一种流水处理双发射处理器记分板电路

技术领域

本发明属于集成电路技术领域,涉及一种流水处理双发射处理器记分板电路。

背景技术

现代超标量RISC处理器设计中,为实现指令的高效发射和处理,使用了双发射指令、流水处理的方式。在指令的译码阶段进行了双发射两条指令之间的相关检测,但仍需保证这两条指令与正在执行单元进行处理的指令不相关。这就需要记分板单元在每次从预译码模块中取出两条指令的同时立即检测与正在执行的指令是否存在相关,以保证发射指令能正确执行。

发明内容

本发明的目的是:

本发明公开了一种流水处理双发射处理器记分板电路,用于判断两条待发射指令是否准备好下发。

本发明的技术解决方案是:

一种流水处理双发射处理器记分板电路,包括:

指令状态表1、寄存器状态表2、功能单元状态表3和状态更新及相关检测逻辑4;

指令状态表1接受预译码模块5中取出的两条待发射指令的对应数据,将数据处理为如下信息:源寄存器、目的寄存器、源操作数ready、目的操作数ready、该指令在执行级所需周期数、所使用操作单元,将所述信息发送至状态更新及相关检测逻辑4;

寄存器状态表2接收功能单元6和译码模块7的数据,将数据处理为模块使用到的64个寄存器的状态信息,所述状态信息表示64个寄存器是否因正在使用而被锁定,将状态信息发送至状态更新及相关检测逻辑4;

功能单元状态表3接收译码模块7的数据,将数据处理为所有执行部件的使用状态信息,包括:该功能单元是否有任务运行和每个任务距离寄存器写回操作的周期数,将所述使用状态信息发送至状态更新及相关检测逻辑4;

状态更新及相关检测逻辑4根据指令状态表1、寄存器状态表2、功能单元状态表3发送的信息共同判断两条待发射指令和正在执行的指令之间是否存在数据相关、功能单元相关或写回通路相关,若三种相关均不存在即可将待发射指令判断为指令准备好;

状态更新及相关检测逻辑4在进行待发射指令与正在执行指令是否存在写回通路相关的判断时,不仅要将待发射指令状态与当前时钟周期正在执行指令的状态进行比较,还要进行下一周期是否相关的预测。

状态更新及相关检测逻辑4中所述相关判断均要在同一周期内完成。

状态更新及相关检测逻辑4中判断的两条待发射指令均与正在执行的指令若不相关时,便在下一周期将两条指令同时下发,该情况下支持流水操作;若仅有一条指令与正在执行的指令不相关,下一周期即可下发一条指令,若两条指令均与正在执行的指令存在相关则等到指令准备好再下发,该两种情况将打断流水周期。

本发明的技术效果是:

本发明提供的一种流水处理双发射处理器记分板电路,能够根据预译码模块提供的两条待发射指令的信息、译码模块提供的两条发射指令的信息以及各个功能单元提供的指令执行完毕的信息,来记录指令、功能单元和寄存器三个状态表,使用上述三个状态表信息,在预译码单元5发出两条指令的同时,流水检测待发射指令与正在执行指令之间是否存在数据相关、功能单元相关和写回通路相关,并为预译码单元5和译码单元7返回指令是否准备好的信息。